Yonga ve donanım tasarımı, karmaşıklığı ve gelişen teknolojilerden kaynaklanan birçok zorluk sunmaktadır. Bu zorluklar, sentez, doğrulama, fiziksel tasarım ve güvenilirlik döngüleri sırasında **performans, güç, alan ve maliyet** (PPAC) optimizasyonu için daha uzun bir **dönüş süreleri** (TAT) ile sonuçlanmaktadır.

Büyük dil modelleri (LLM’ler), doğal dili büyük ölçekte anlama ve üretme konusundaki olağanüstü yetenekleri sayesinde çeşitli alanlarda birçok potansiyel uygulama ve fayda sunmaktadır. Donanım tasarımı için LLM tabanlı yapay zeka ajanlarının başarılı bir şekilde kullanılması, **TAT’yi** önemli ölçüde azaltarak daha hızlı ürün döngüleri, daha düşük maliyetler, geliştirilmiş tasarım güvenilirliği ve hata riskinin azaltılması gibi kazanımlar sağlayabilir.

Marco: Esnek Grafik Tabanlı Görev Çözümü ve Çoklu YZ Ajanları Çerçevesi

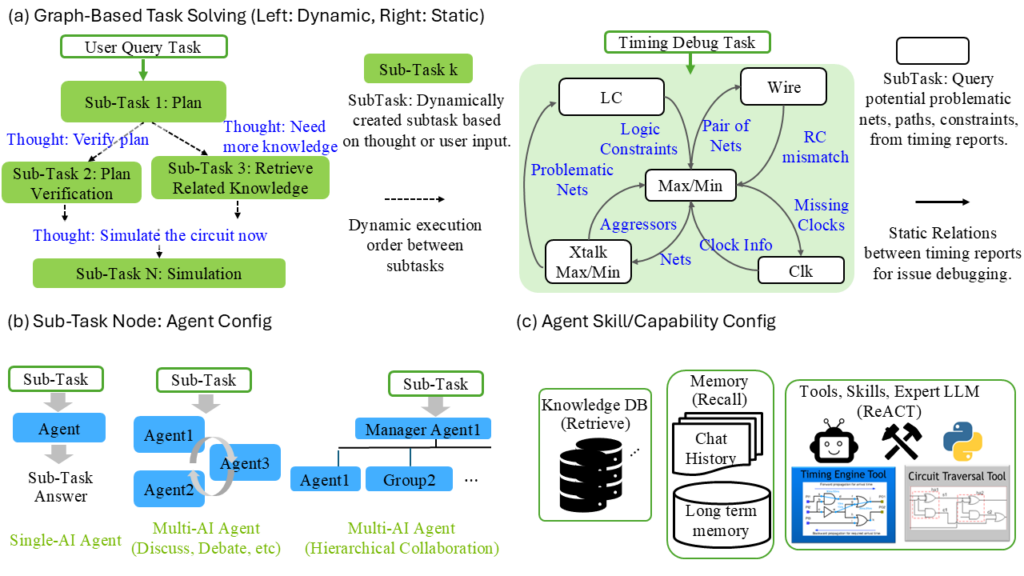

Önerilen Marco çerçevesini tanıtıyoruz. Bu çerçeve, grafik tabanlı görev çözümü, alt görevler için ajan yapılandırmaları ve her yapay zeka ajanı için yetenek/araç yapılandırmalarını gerçek zamanlı olarak kapsamaktadır.

Şekil 1, çip tasarım bilgisi (örneğin, devreler, zamanlama vb.) ile esnek bir şekilde entegre edilen dinamik ve statik yapılandırılabilir grafik tabanlı görev çözümünü göstermektedir.

Görev grafiğinde, her düğüm bir alt görevi temsil ederken, her kenar düğümler arasındaki yürütme veya bilgi ilişkisini temsil etmektedir. Her alt görev için, Autogen kullanarak tek YZ veya çoklu YZ ajanlarını bilgi veritabanı, araçlar ve hafıza ile yapılandırabilirsiniz.

Tablo 1, Marco çerçevesinde çeşitli ajanlar için görev grafi, ajan ve LLM yapılandırmalarını özetlemektedir. VerilogCoder ve MCMM zamanlama analizi ajanı, sırasıyla spesifikasyondan RTL’ye geçiş ve zamanlama raporlarından önemli noktaların çıkarılmasında dinamik bir görev grafi kullanmaktadır. Zamanlama yolu hata ayıklama ajanı, statik zamanlama hata ayıklama görev grafi aracılığıyla sorunlu ağları, telleri ve kısıtlamaları bulmaktadır (Şekil 1).

| Ajan Çalışmaları | Görev Kategorisi | Marco Çerçevesi Yapılandırması | ||

| Görev Grafiği | Alt Görev Ajan Yapılandırması | Özelleştirilmiş Araçlar | ||

| RTLFixer | Kod Sözdizimi Düzeltme | N/A | Tek YZ | RTL Sözdizimi Hatası RAG Veritabanı |

| Standart Hücre Tasarım Optimizasyonu | Optimizasyon | N/A | Tek YZ | Küme Değerlendirici, Netlist Geçiş Aracı |

| MCMM Zamanlama Analizi (Bölüm/Dinamik Seviyesi) | Özet ve Anomali Belirleme | Dinamik | Çoklu YZ | Zamanlama Dağılımı Hesaplayıcı, Zamanlama Metrik Kıyaslayıcı |

| DRC Kodu | Kod Üretimi | N/A | Çok Modlu & Çoğul YZ | Kuralların Analizi, Yerleşim DRC Analizi, DRC Kodu Değerlendirmesi |

| Zamanlama Yolu Hatası Ayıklama (Yol Seviyesi) | Özet ve Anomali Belirleme | Statik | Hiyerarşik Çoklu YZ | Ajanik Zamanlama Raporu Alma |

| VerilogCoder | Kod Üretimi | Dinamik | Çoklu YZ | TCRG Alma Aracı, AST Tabanlı Dalga Biçimi İzleme Aracı |

Tablo 1’de, RTLFixer ve Standart Hücre Tasarım Optimizasyonu ajanları (yani, tek YZ yapılandırması) için Marco çerçevesinin destek sağladığı görülmektedir. Diğer çoklu YZ ajanları ise Marco çerçevesinde uygulanmaktadır.

RTLFixer, standart hücre tasarım optimizasyonu için LLM ajanı ve DRC Kodu için özelleştirilmiş araçlar, hafıza ve alan bilgileri ile tek YZ veya çoklu YZ ajan konfigürasyonları kullanılmıştır.

Otomatik Donanım Tanım Dilleri Kod Üretimi

Otonom ajanların etkili olduğu bir alan, donanım tanım dilleri (HDL’ler), örneğin Verilog kodunun üretilmesidir. VLSI tasarımının artan karmaşıklığı nedeniyle, Verilog ve VHDL yazmak zaman alıcı ve hatalara açıktır, bu da işlevsel doğruluğun debug edilmesi için birden çok iterasyona gereksinim duyar. Bu nedenle, donanım spesifikasyonlarını tamamlama sürecinde tasarım maliyetlerini ve tasarımcı çabasını azaltma ihtiyacı kritik bir gereksinim olarak ortaya çıkmıştır.

LLM’ler doğal dil tanımlarından Verilog kodu üretebilir. Ancak LLM’ler, genellikle hem sentaktik hem de işlevsel olarak doğru kod üretmede zorluklar yaşayabilir.

Sözdizimi Doğruluğu

RTLFixer, LLM’lerin sözdizimi hatalarını iteratif olarak debug ve düzeltmeler yapabilmesini sağlamak için bildirim artırma (RAG) ve ReAct istemlerini birlikte kullanmaktadır. RAG, hata düzeltme için bağlam sağlamak amacıyla insan uzman rehberliği veritabanı kullanır. ReAct, LLM’nin hatayı anlamasını, düzeltmeyi planlamasını ve planını uygulamasını sağlar.

Fonksiyonel Doğruluğu

VerilogCoder, Verilog kodunu üretmek ve debug etmek için bir görev planlayıcı ve soyut sözdizim ağacı (AST) tabanlı dalga biçimi izleme aracı içeren çoklu ajan sistemidir. Görevleri yönetilebilir alt görevlere ayırmak ve her adımda sinyal geçişlerini bağlamak için bir görev ve devre ilişkisi grafiği (TCRG) kullanmaktadır (Şekil 2).

Ayrıca, bir AST tabanlı dalga biçimi izleme aracı, LLM ajanının işlevsel hataları tanımlayıp düzeltmesine yardımcı olur. VerilogCoder, VerilogEval-Human v2 benchmark’ında %94.2 başarı oranı elde ederek önceki yöntemlere göre önemli bir iyileşme sağlamaktadır.

Videoda, VerilogCoder’ın fonksiyonel olarak doğru Verilog kodunu TCRG planlama ve AST tabanlı dalga biçimi izleme araçları ile otonom olarak tamamladığı gösterilmektedir.

Otomatik DRC Yerleşim Kod Üretimi

DRC-Coder, DRC ve Yerleşim DRV analiz araçları ile çoklu otonom ajanlar kullanarak DRC kodu üretmektedir. Sistem, tasarım kurallarını metinsel tanımlamalardan, görsel illüstrasyonlardan ve yerleşim temsilinden yorumlamaktadır. Çoklu LLM ajanları, kuralları yorumlayan bir planlayıcı ve kuralları yürütülebilir koda dönüştüren bir programcı içerir.

DRC-Coder, üretilen kodu iyileştirmek için kod değerlendirmesinden gelen geri bildirimleri kullanarak bir **oto debug** süreci eklemiştir.

Videoda, DRC-Coder’ın bir yerleşim analiz aracı, oto-debug süreci ve çok modlu ile çoklu YZ ajanlarının yeteneklerini kullanarak DRC kodunu nasıl ürettiği gösterilmektedir.

DRC-Coder, 3nm altındaki bir teknoloji düğümü için DRC kodu üretirken mükemmel F1 puanı (1.000) elde etmektedir. Önerilen otomatik ajan yaklaşımı, DRC kodu oluşturma süresini haftalardan ortalama dört dakikaya düşürürken standart istem tekniklerini geride bırakmıştır.

Standart Hücre Tasarımı Optimizasyonu

Standart hücre tasarımı optimizasyonu için LLM ajanı, doğal dil ve mantık becerilerini kullanarak uluşuk alan senaryoları için yüksek kaliteli küme kısıtlarını aşamalı olarak oluşturarak hücre yerleşimi PPAC’sini optimize etmektedir. Sistem, net bilgilerini ve hücre yerleşimi analizini kullanarak MOSFET cihazlarını kümelere gruplandırmaktadır. AI ajanı, %19.4 daha küçük hücre alanına ulaşırken, Dönüştürücü tabanlı cihaz kümelerinin yaklaşımına göre %23.5 daha fazla LVS ve DRC temiz hücre yerleşimleri üretmektedir.

Çok Açılı Çoklu Mod Zamanlama Raporu Hata Ayıklama ve Analizi

Çok köşeli çoklu mod (MCMM) zamanlama analizi ajanı, spesifikasyondan RTL’ye geçişi tamamlamak ve zamanlama raporlarından önemli noktaları çıkarmak için dinamik görev grafiklerini kullanmaktadır.

MCMM zamanlama analizi ajanı, bir dizi endüstriyel vakada deneyimli mühendislerin değerlendirilmesine dayanan ortalama 8.33 puan elde ederken, insan mühendislerine göre yaklaşık **60 kat** hız artışları sağlamaktadır (Şekil 3).

Zamanlama yolu hata ayıklama ajanı, statik zamanlama hata ayıklama görev grafi aracılığıyla sorunlu ağları, telleri ve kısıtlamaları bulmaktadır.

Tablo 2’de, zamanlama yolu hata ayıklama ajanının %86 oranında geçme oranıyla görevleri çözme başarısı gösterdiği, standart görev çözme yaklaşımının ise hiçbir görevi çözemediği görülmektedir.

| Çoklu Rapor Görev Tanımı | Gerekli AnalizAlt-Görevler | Standart Görev Çözümü | Zamanlama Yolu Hata Ayıklayıcı Ajanı |

| Yükseliş/alçalış bilgisi olmayan eksik clk sinyallerini bul | max, clk | X | V |

| Yüksek RC uyumsuzluk olan ağ çiftlerini tanımak | max, wire | X | V |

| Kurban ile agresifler arasındaki olağandışı kısıtları tespit et | max, xtalk, LC | X | V |

| Kurban ile agresifler arasındaki olağandışı RC değerlerini tanı | max, wire, xtalk, LC | X | V |

| En yüksek RC değerlere sahip en yavaş aşamaları bul | max, wire, xtalk, LC | X | V |

| Her zamanlama tablosunu aşama, nokta değerleri ve zamanlama uyumsuzlukları için karşılaştır | max | X | X |

| Path listesindeki belirli aşamalar için Görev M2 ve Görev M3 | max, wire, xtalk, LC | X | V |

| Ortalama Geçme Oranı | %0 | %86 | |

X=Görevi çözemedi. V=Görevi başarıyla çözdü.

Sonuçlar

Önerilen Marco çerçevesi, gerçek zamanlı donanım tasarım görevlerinin çözümü için daha esnek ve alan odaklı yöntemleri mümkün kılmaktadır. Görev grafi ve esnek tek YZ ve çok YZ ajan yapılandırmaları ile alan spesifik araçlar ve bilgiler kullanarak, hücre yerleşimi optimizasyonu, Verilog sözdizimi hatası düzeltme, Verilog ve DRC kodu üretimi, sorunlu bloklar, ağlar ve teller üzerindeki zamanlama hata ayıklama gibi çeşitli görevler için farklı ajanlar geliştirilmiştir.

Deneysel sonuçlar, çip tasarımı için işbirlikçi LLM tabanlı ajanların kullanımında etkileyici performans ve verimlilik kazançları göstermektedir.

Donanım tasarımında ajans araştırmalarının gelecekteki yönleri şunları içermektedir:

- Yüksek kaliteli donanım tasarım verileri ile LLM’leri eğitim

- Donanım sinyal ve dalga biçimi hata ayıklamada LLM tabanlı ajanların yeteneklerini artırma

- Tasarım akışına PPAC metriklerini dahil etme

- Daha karmaşık donanım görevlerini çözmek için daha etkili kendi kendine öğrenme teknikleri ve hafıza sistemleri geliştirme

Daha fazla kağıt ve projeler için otomatik tasarım üzerine, NVIDIA Tasarım Otomasyonu Araştırma Grubu sayfasını ziyaret edebilirsiniz.

Bu yazıda vurgulanan teknolojilere ilgi duyanlar için, ilgili kağıtların listesi:

- RTLFixer: Büyük Dil Modelleri ile RTL Sözdizim Hatalarını Otomatik Olarak Düzeltme

- /NVlabs/RTLFixer Github deposu

- VerilogCoder: Grafik Tabanlı Planlama ve Soyut Sözdizim Ağacı (AST) Tabanlı Dalga Biçimi İzleme Aracı ile Otonom Verilog Kodlama Ajanları

- /NVlabs/VerilogCoder Github deposu

- DRC-Coder: LLM Otonom Ajanı Kullanarak Otomatik DRC Kontrol Kod Üretimi

- Büyük Dil Modeli (LLM) ile Standart Hücre Yerleşim Tasarım Optimizasyonu