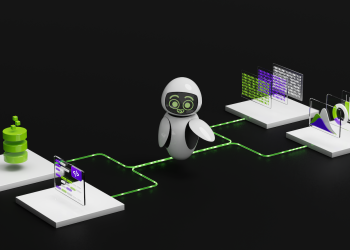

Intel’in Yeni Mimarisinin Detayları Ortaya Çıktı

Intel’in Arrow Lake mimarisine ait yonga görüntüleri yayınlandı ve bu, şirketin chiplet (kısmı) tasarımını tüm ayrıntılarıyla gözler önüne seriyor. Andreas Schiling, Arrow Lake’a ait birkaç görüntü paylaşarak mimarinin bireysel tile yapılarını ve compute tile içindeki çekirdeklerin düzenini ortaya koydu.

Die Yapısının Ayrıntıları

İlk görüntüde, Intel’in masaüstü Core Ultra 200S serisi CPU’larının tam die yapısı görünmekte. Compute tile üst solda, IO tile altta, SoC tile ve GPU tile ise sağda yer alıyor. Alt sol ve üst sağda ise yapısal sağlamlık sağlamak amacıyla yerleştirilmiş iki filler die bulunuyor.

Compute die, TSMC’nin en son nesil N3B düğümünde üretilmiş olup toplam alanı 117.241 mm²’dir. IO tile ve SoC tile ise TSMC’nin eski N6 düğümünde üretilmiştir; IO tile 24.475 mm² ve SoC tile 86.648 mm² ölçülerindedir. Tüm bu parçalar, Intel’in 22nm FinFET düğümünde üretilmiş olan altında yatan bir base tile üzerinde yer alıyor. Arrow Lake, rakip bir firmanın düğümleri kullanılarak üretilmiş olan Intel’in ilk mimarisi olma özelliğini taşıyor.

Bağlantı ve Yapılandırma Güncellemeleri

Bir sonraki görüntü, Arrow Lake’daki ikinci düzlemin tüm alt bileşenlerini gösteriyor. IO die, Thunderbolt 4 denetleyici/görüntü PHY’sını, PCIe Express buffer/PHY’leri ve TBT4 PHY’lerini barındırıyor. SoC tile ise görüntü motorları, medya motoru, daha fazla PCIe PHY, bufferlar ve DDR5 bellek denetleyicilerini içeriyor. GPU tile’da ise dört Xe GPU çekirdeği ve bir Xe LPG (Arc Alchemist) render dilimi bulunmakta.

Son görüntüde Intel’in Arrow Lake için en yeni çekirdek yapılandırması sergilenmekte. Bu yapılandırma, önceki Intel mimarilerinden farklılık gösteriyor. Intel, E-core çekirdeklerini P-core çekirdeklerinin arasına yerleştirerek ısı noktalarını azaltmayı hedefledi. Sekiz P-core’un dörtü die’ın kenarında, diğer dörtü ise ortasında yer alırken, dört E-core kümesi (her biri dört çekirdek ihtiva ediyor) dış ve iç P-core’ların arasında konumlandırılmış.

Schilling’in die görüntüsü ayrıca Arrow Lake için cache yapısını da ortaya koyuyor. Her P-core için 3MB L3 cache (toplamda 36MB) ve her E-core kümesi için 3MB L2 cache mevcut. Bu iki L2 cache kümesi ve bağlı çekirdekler arasında bir interconnect bulunmakta, ayrıca her çekirdek kümesini ring agent ile bağlamak da bu bağlantının sorumluluğunda. Intel’in Arrow Lake ile yaptığı en büyük güncellemelerden biri, E-core kümelerini P-core’lara ait L3 cache ile bağlayarak onlara da L3 cache sağlamak oldu.

Intel’in Gelecek Planları

Arrow Lake, Intel’in bugüne kadar geliştirdiği en karmaşık mimarilerden biri ve masaüstü pazarında ilk chiplet tasarımını sunuyor. Ancak, Intel’in masaüstü chiplet tabanlı ilk rakibi **şu anda sınırlı bir kabul gördü**; bunun nedeni, bu kısımların birbirine bağlanmasını sağlayan interconnect üzerinden yaşanan gecikme sorunları. Intel, bu sorunu yazılım güncellemeleri ile çözmeye çalışıyor. Yine de, mevcut uygulaması AMD’nin Ryzen 9000 CPU’ları (özellikle 9800X3D dahil) ile rekabet edebilecek düzeyde değil ve hatta kendi önceki 14. nesil işlemcilerini (örneğin, 14900K) oyun performansında geçemiyor.

Tüm bunların yanı sıra, chiplet yaklaşımına geçiş, Intel’in yapılarını gelecekte daha verimli bir şekilde optimize etmesine olanak tanıyacak. Her bir tile, diğerlerinden bağımsız olarak geliştirilebilmekte ve farklı düğümlerle üretilerek verimliliği artırmakta, geliştirmeleri optimize etmekte ve üretim maliyetlerini düşürmektedir.